# **TCG D-RTM Architecture**

Document Version 1.0.0 June 17, 2013

Contact: <a href="mailto:admin@trustedcomputinggroup.org">admin@trustedcomputinggroup.org</a>

# **Published**

Copyright © TCG 2007-2013

#### **Disclaimers**

- THE COPYRIGHT LICENSES SET FORTH DOES NOT REPRESENT ANY FORM OF LICENSE

OR WAIVER, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, WITH RESPECT TO

PATENT RIGHTS HELD BY TCG MEMBERS (OR OTHER THIRD PARTIES) THAT MAY BE

NECESSARY TO IMPLEMENT THIS SPECIFICATION OR OTHERWISE. Contact TCG

Administration (admin@trustedcomputinggroup.org) for information on specification licensing

rights available through TCG membership agreements.

- THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO EXPRESS OR IMPLIED WARRANTIES

WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A

PARTICULAR PURPOSE, ACCURACY, COMPLETENESS, OR NONINFRINGEMENT OF

INTELLECTUAL PROPERTY RIGHTS, OR ANY WARRANTY OTHERWISE ARISING OUT OF

ANY PROPOSAL, SPECIFICATION OR SAMPLE.

- Without limitation, TCG and its members and licensors disclaim all liability, including liability for

infringement of any proprietary rights, relating to use of information in this specification and to the

implementation of this specification, and TCG disclaims all liability for cost of procurement of

substitute goods or services, lost profits, loss of use, loss of data or any incidental, consequential,

direct, indirect, or special damages, whether under contract, tort, warranty or otherwise, arising in

any way out of use or reliance upon this specification or any information herein.

Any marks and brands contained herein are the property of their respective owners.

# Acknowledgements

The TCG would like acknowledge the contributions of the many individuals (listed below) and the companies who allowed them to volunteer their time to the development of this specification.

The chairs of the D-RTM working group deserve special thanks, they include Monty Wiseman, and Lee Wilson.

Special thanks are given to the editors of this specification: David Wooten, Rob Spiger, and David Robinson.

#### **Contributors**

Jacob Shin; AMD

Bill Jacobs; Cisco

Mark Scott-Nash; Intel

David Robinson; Microsoft

Dennis Mattoon; Microsoft

Eugene Myers; US Govt

Louis Hobson; HP

Graeme Proudler; HP

Geoffrey Strongin; AMD

Mukund Khatri; Dell

Varugis Kurien; Microsoft

Julian Hammersley; AMD

Shiva Dasari; IBM

Monty Wiseman; Intel

Rob Spiger; Microsoft

Dick Wilkins; Phoenix Tech

Ron Perez; AMD

Ralf Findeisen; AMD

David Challener; Johns-Hopkins

Hidenobu Ito; Fujitsu

Dalvis Desselle; HP

Steve Goodman; Lenovo

Gary Simpson; AMD Lee Wilson; IBM Kirk Brannock; Intel David Wooten; Microsoft Eric Paris; Red Hat Amy Nelson; Dell Mark Piwonka; HP Conan Dailey; General Dynamics

Will Burton; CESG Randy Springfield; Lenovo Timothy Markey; Phoenix

# Contents

| 1 | Intro | ducti  | on to This Document                            | 10 |

|---|-------|--------|------------------------------------------------|----|

|   | 1.1   | Ove    | rview                                          | 10 |

|   | 1.2   | Doc    | ument Structure                                | 10 |

|   | 1.3   | Ref    | erences                                        | 11 |

|   | 1.4   | Ten    | ns and Definitions                             | 11 |

| 2 | Archi | itectu | ıral Overview                                  | 18 |

|   | 2.1   | Intro  | oduction                                       | 18 |

|   | 2.2   | DM     | Α                                              | 18 |

|   | 2.3   | Sys    | tem Management Mode (SMM)                      | 19 |

|   | 2.4   | Non    | -Host Platforms                                | 19 |

|   | 2.5   | TCE    | 3 Hardware Protection                          | 20 |

|   | 2.6   | Adv    | anced Configuration and Power Interface (ACPI) | 20 |

|   | 2.7   | Auth   | norities                                       | 20 |

|   | 2.8   | PCF    | R Measurements                                 | 20 |

|   | 2.9   | DC     | E and the DCE Preamble                         | 21 |

|   | 2.9.  | 1      | The "Gap"                                      | 21 |

|   | 2.9.  | 2      | Timeline                                       | 22 |

|   | 2.9.  | 3      | Conclusion                                     | 23 |

| 3 | Trust | ted C  | Computing Base                                 | 24 |

|   | 3.1   | Intro  | oduction                                       | 24 |

|   | 3.2   | DM     | A (Direct Memory Access)                       | 24 |

|   | 3.2.  | 1      | DMA Requirements                               | 24 |

|   | 3.3   | Sys    | tem Management Mode                            | 24 |

|   | 3.3.  | 1      | Protecting SMM                                 | 25 |

|   | 3.3.  | 2      | SMM Requirements                               | 26 |

|   | 3.4   | Non    | -Host Platforms                                | 27 |

|   | 3.4.  | 1      | Requirements for Non-Host Platforms            | 28 |

|   | 3.5   | Peri   | pherals                                        | 28 |

|   | 3.5.  | 1      | Peripheral Requirements                        | 28 |

|   | 3.6   | TPN    | Л                                              | 28 |

|   | 3.6.  | 1      | TPM Requirements                               | 28 |

|   | 3.7   | TPN    | /I Interface                                   | 29 |

|   | 3.7.  | 1      | TPM Interface Requirements                     | 29 |

|   | 3.8   | S-R    | TM                                             | 29 |

|   | 3.8.  | 1      | S-RTM Requirements                             | 29 |

|   | 3.8.2    | S-CRTM Validation                                 | 29 |

|---|----------|---------------------------------------------------|----|

|   | 3.8.3    | S-RTM Update Requirements                         | 29 |

|   | 3.8.4    | S-RTM S3 Resume                                   | 29 |

|   | 3.9 Se   | ensitive Resources                                | 30 |

|   | 3.9.1    | Sensitive Resource Definition                     | 30 |

|   | 3.9.2    | Sensitive Resource Granularity                    | 30 |

|   | 3.9.3    | Sensitive Resources Requirements                  | 30 |

|   | 3.10 M   | emory Map                                         | 31 |

|   | 3.10.1   | Memory Map Requirements                           | 31 |

|   | 3.11 A   | CPI Name Space                                    | 31 |

|   | 3.11.1   | ACPI Requirements                                 | 31 |

|   | 3.11.2   | Protection from AML                               | 32 |

|   | 3.12 Po  | ower State Transitions                            | 32 |

|   | 3.12.1   | Power State Transition Requirements               | 32 |

|   | 3.13 DI  | _ME                                               | 33 |

|   | 3.14 D   | CE Preamble                                       | 33 |

|   | 3.14.1   | Preamble Requirements                             | 33 |

|   | 3.15 DI  | _ME_Exit                                          | 33 |

|   | 3.15.1   | DLME_Exit Requirements                            | 33 |

|   | 3.16 CI  | PU Microcode Updates                              | 34 |

|   | 3.17 D   | namic Core Root of Trust for Measurement (D-CRTM) | 34 |

|   | 3.17.1   | Definition                                        | 34 |

|   | 3.17.2   | D-CRTM Requirements                               | 34 |

| 4 | Structur | es                                                | 36 |

|   | 4.1 In   | troduction                                        | 36 |

|   | 4.2 D-   | RTM Resources Table Structure                     | 36 |

|   | 4.2.1    | Description                                       | 36 |

|   | 4.2.2    | Table Structure                                   | 37 |

|   | 4.2.3    | D-RTM Resources Table Header                      | 37 |

|   | 4.2.4    | DL_Entry_Base                                     | 38 |

|   | 4.2.5    | DL_Entry_Length                                   | 38 |

|   | 4.2.6    | DL_Entry32                                        | 38 |

|   | 4.2.7    | DL_Entry64                                        | 38 |

|   | 4.2.8    | DLME_Exit                                         | 38 |

|   | 4.2.9    | Log Area                                          | 38 |

|   | 4.2.10   | Architecture_Dependent                            | 38 |

|   | 4.3 D-   | RTM Resources Table Flags (DRT_Flags)             | 38 |

| _ |          |                                                   |    |

| 4.3.1        | Validated_Tables_List                                      | 39           |

|--------------|------------------------------------------------------------|--------------|

| 4.4 Re       | source Descriptor Structure                                | 39           |

| 4.4.1        | Resources_List                                             | 40           |

| 4.4.2        | DLME_PlatformSpecificIds_Supported                         | 40           |

| 4.5 DF       | RTM_PUBLIC_KEY Structure                                   | 40           |

| 4.5.1        | Description                                                | 40           |

| 4.5.2        | Structure Definition                                       | 41           |

| 4.5.3        | Structure Fields                                           | 41           |

| 4.6 DL       | ME_DESCRIPTOR Structure                                    | 41           |

| 4.6.1        | Description                                                | 41           |

| 4.6.2        | Structure Definition                                       | 42           |

| 4.6.3        | Structure Field Definitions                                | 42           |

| 4.7 DF       | RTM_ACPI_TABLES                                            | 43           |

| 4.7.1        | Description                                                | 43           |

| 4.7.2        | Structure Definition                                       | 44           |

| 4.7.3        | Structure Field Definitions                                | 44           |

| 4.8 DL       | ME_ARGUMENTS Structure                                     | 44           |

| 4.8.1        | Description                                                | 44           |

| 4.8.2        | Structure Definition                                       | 44           |

| 4.8.3        | Structure Field Definitions                                | 45           |

| 4.9 DL       | ME_TRANSLATION_LIST Structure                              | 45           |

| 4.9.1        | Description                                                | 45           |

| 4.9.2        | Structure Definition                                       | 45           |

| 4.9.3        | Structure Field Definitions                                | 46           |

| 5 System     | States, Transitions, and Interfaces                        | 47           |

| 5.1 Int      | roduction                                                  | 47           |

| 5.2 Sy       | stem States                                                | 50           |

| 5.2.1        | Pre-Gap                                                    | 50           |

| 5.2.2        | Pre-OS Environment                                         | 50           |

| 5.2.3        | The Gap                                                    | 50           |

| 5.2.4        | S-RTM OS Present Environment                               | 50           |

| 5.2.5        | D-RTM Configuration Environment (DCE)                      | 51           |

| 5.2.6        | Remediation Environment                                    | 51           |

| 5.2.7        | Dynamic Operating System Environment                       | 51           |

| 5.3 Sy       | stem State Transitions, Requirements, and Interfaces       | 51           |

| 5.3.1        | Pre-Gap Transition to the Gap                              | 51           |

| 5.3.2        | The Pre-OS Environment to the S-RTM OS Present Environment | 51           |

| April 20, 20 | 13 DUBUSHED                                                | Page 5 of 03 |

|   | 5.3. | 3     | The Gap to the DCE Preamble                                                          | 51 |

|---|------|-------|--------------------------------------------------------------------------------------|----|

|   | 5.3. | 4     | The DCE to the DLME                                                                  | 56 |

|   | 5.3. | 5     | The DLME to DLME_Exit                                                                | 64 |

|   | 5.3. | 6     | The S-RTM OS Present Environment to S3                                               | 65 |

|   | 5.3. | 7     | S3 to the S-RTM OS Present Environment                                               | 66 |

|   | 5.3. | 8     | The Dynamic Operating System Environment to S3                                       | 66 |

|   | 5.3. | 9     | S3 to the Dynamic Operating System Environment                                       | 66 |

|   | 5.3. | 10    | S-RTM OS Present Environment to S4/S5                                                | 66 |

|   | 5.3. | 11    | The Dynamic Operating System Environment to S4/S5                                    | 66 |

| 6 | PCR  | Usa   | ge                                                                                   | 67 |

|   | 6.1  | D-R   | TM PCR Values and PCR Reset                                                          | 67 |

|   | 6.2  | Det   | ail and Authority Measurements                                                       | 67 |

|   | 6.3  | DCI   | E Authority Measurement Special Case                                                 | 68 |

|   | 6.4  | DCI   | E Component Revocation                                                               | 68 |

|   | 6.5  | D-R   | TM PCR Defined in This Specification                                                 | 68 |

|   | 6.6  | Det   | ail and Authority Measurement Definitions                                            | 69 |

|   | 6.6. | 1     | Details Measurement                                                                  | 69 |

|   | 6.6. | 2     | Authority Measurement                                                                | 69 |

|   | 6.7  | The   | Limited Set of Known PCR.Authorities Values                                          | 70 |

| 7 | DCE  | Req   | uirements                                                                            | 71 |

|   | 7.1  | Intro | oduction                                                                             | 71 |

|   | 7.2  | D-C   | RTM                                                                                  | 71 |

|   | 7.3  | Cor   | figuration Description Validation                                                    | 71 |

|   | 7.4  | Vali  | dation and Measurement                                                               | 71 |

|   | 7.5  | Ren   | nediation                                                                            | 71 |

| 8 | Com  | pone  | ent Setup, Configuration, Validation, and Measurement Required for the D-RTM Process | 72 |

|   | 8.1  | Intro | oduction                                                                             | 72 |

|   | 8.2  | DM    | A                                                                                    | 72 |

|   | 8.2. | .1    | Setup and Configuration                                                              | 72 |

|   | 8.2. | 2     | Validation and Measurement                                                           | 72 |

|   | 8.3  | SMI   | М                                                                                    | 72 |

|   | 8.3. | .1    | Setup and Configuration                                                              | 72 |

|   | 8.3. | 2     | Validation and Measurement                                                           | 73 |

|   | 8.4  | Nor   | n-Host Platform                                                                      | 74 |

|   | 8.4. | 1     | Setup and Configuration                                                              | 74 |

|   | 8.4. | 2     | Validation and Measurement                                                           | 75 |

|   | 8.5  | Per   | ipherals                                                                             | 75 |

|   |      |       |                                                                                      |    |

|   | 8.5.1    | Setup and Configuration                                    | 75 |

|---|----------|------------------------------------------------------------|----|

|   | 8.5.2    | Validation and Measurement                                 | 75 |

|   | 8.6 TPI  | М                                                          | 75 |

|   | 8.6.1    | Setup and Configuration                                    | 75 |

|   | 8.6.2    | Validation and Measurement                                 | 75 |

|   | 8.7 DC   | E Measurement                                              | 75 |

|   | 8.8 Pla  | tform S-RTM                                                | 76 |

|   | 8.8.1    | Setup and Configuration                                    | 76 |

|   | 8.8.2    | Validation and Measurement                                 | 76 |

|   | 8.9 Ser  | nsitive Resources                                          | 76 |

|   | 8.9.1    | Setup and Configuration                                    | 76 |

|   | 8.9.2    | Validation and Measurement                                 | 76 |

|   | 8.10 Mei | mory Map                                                   | 76 |

|   | 8.10.1   | Setup and Configuration                                    | 76 |

|   | 8.10.2   | Validation and Measurement                                 | 76 |

|   | 8.11 AC  | PI Name Space                                              | 76 |

|   | 8.11.1   | Setup and Configuration                                    | 76 |

|   | 8.11.2   | Validation and Measurement                                 | 77 |

|   | 8.12 Pov | ver State Transitions                                      | 77 |

|   | 8.12.1   | Setup and Configuration                                    | 77 |

|   | 8.12.2   | Validation and Measurement                                 | 77 |

|   | 8.13 DLI | ME                                                         | 77 |

|   | 8.13.1   | Setup and Configuration                                    | 77 |

|   | 8.13.2   | Validation                                                 | 77 |

|   | 8.13.3   | Measurement                                                | 79 |

|   | 8.14 CP  | U and Microcode Updates                                    | 79 |

|   | 8.14.1   | Setup and Configuration                                    | 79 |

|   | 8.14.2   | Validation                                                 | 79 |

|   | 8.14.3   | Measurement                                                | 79 |

| 9 | Event Lo | gging and Reporting                                        | 80 |

|   | 9.1 DC   | E Log                                                      | 80 |

|   | 9.1.1    | Introduction                                               | 80 |

|   | 9.1.2    | Log Format                                                 | 80 |

|   | 9.1.3    | ACPI Table Usage and Measurement Log Location and Lifetime | 80 |

|   | 9.1.4    | Measurement Log Location in Memory                         | 80 |

|   | 9.1.5    | Measurement Log Initialization                             | 81 |

|   | 9.1.6    | Scope of PCR measurements in the log                       | 81 |

|   |          |                                                            |    |

|   | 9.1 | .7   | Measured Events                                                  | 81 |

|---|-----|------|------------------------------------------------------------------|----|

| 4 | D-R | TM E | xample Implementations                                           | 82 |

|   | A.1 | Dis  | claimer                                                          | 82 |

|   | A.2 | Tax  | onomy of a D-RTM Capable BIOS                                    | 82 |

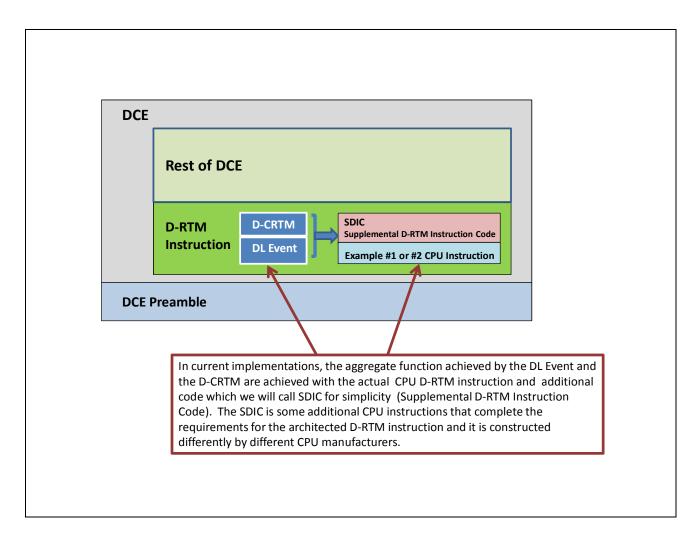

|   | A.2 | .1   | A Few Comments on D-RTM Instructions, DL Event, and D-CRTM       | 82 |

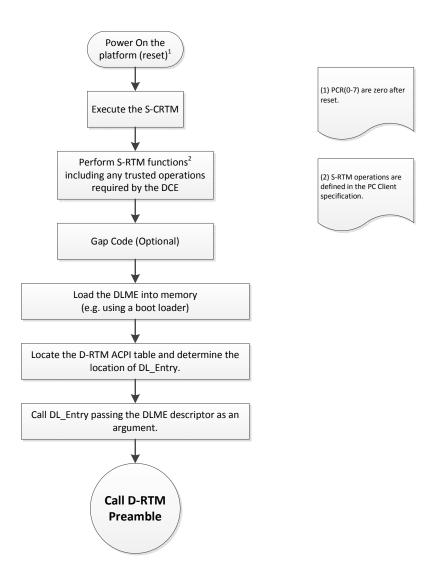

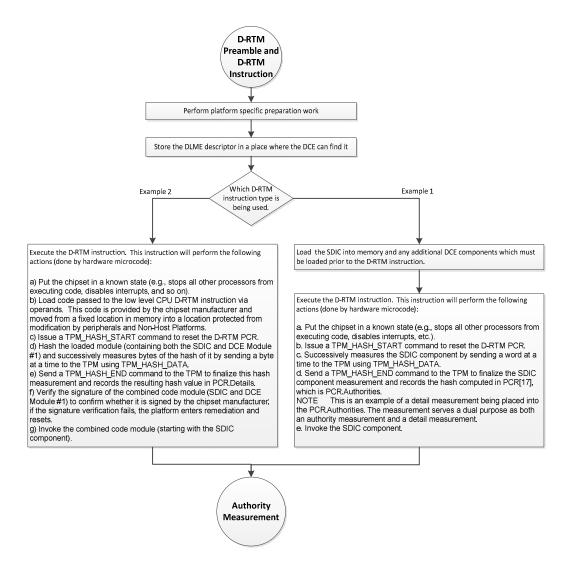

|   | A.2 | .2   | Initial Common Steps Taken by Both D-RTM Example Implementations | 83 |

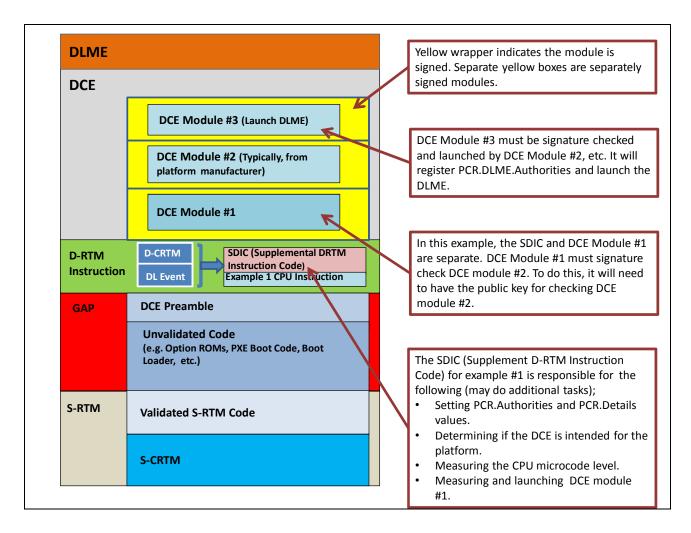

|   | A.2 | 3    | D-RTM Implementation Example #1                                  | 84 |

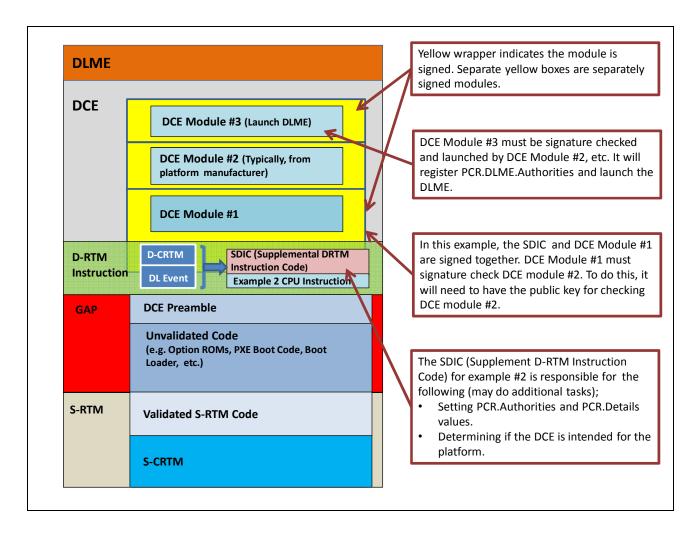

|   | A.2 | .4   | D-RTM Implementation Example #2                                  | 85 |

|   | A.2 | .5   | Final Common Steps Taken by Both D-RTM Example Implementations   | 87 |

|   | A.2 | .6   | Steps Taken to Exit the Measured DLME Environment                | 87 |

|   | A.2 | .7   | What Should PCR.Authorities Be Set To?                           | 87 |

|   | A.3 | S-C  | RTM To D-RTM Preamble                                            | 88 |

|   | A.4 | D-F  | TM Preamble and Instruction                                      | 89 |

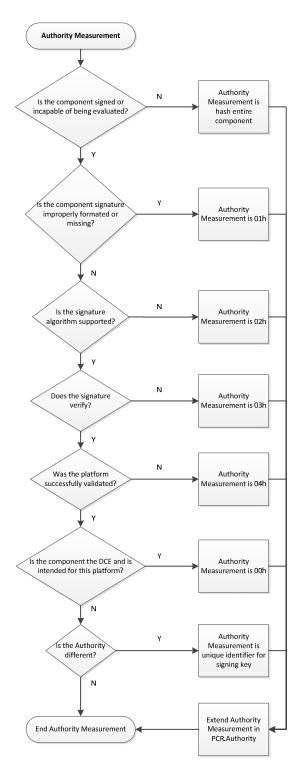

|   | A.5 | Aut  | nority Measurement                                               | 90 |

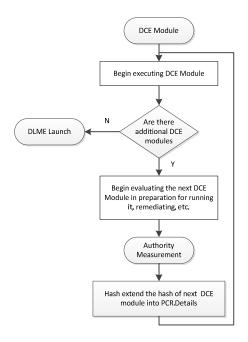

|   | A.6 | Add  | litional DCE Module Execution                                    | 91 |

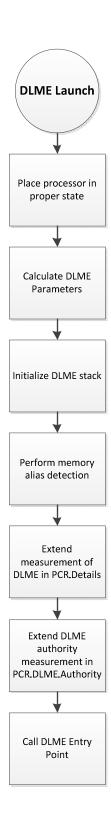

|   | A.7 | DLN  | ∕/E Launch                                                       | 92 |

April 20, 2013 Page 8 of 93 PUBLISHED

Page 9 of 93 April 20, 2013 PUBLISHED

# 1 Introduction to This Document

## 1.1 Overview

This specification describes the architecture and implementation examples for a Dynamic Root of Trust for Measurement (D-RTM) used for measured platform initialization without a hardware platform restart. This specification extends the TCG PC Client specification (See (1)). The term "dynamic" is used because the measured platform initialization may occur while the hardware platform is running. In contrast, the Static Root of Trust for Measurement (S-RTM) requires a platform shutdown or restart.

## 1.2 Document Structure

The document's chapters describe certain aspects of a D-RTM. The document begins with a description of architectural objectives and basic architectural elements. An overview of the D-RTM environment and goals is given. Following chapters describe important aspects of the environment and what influence on a platform implementation the use and support for a D-RTM has. This is followed by a description of the D-RTM architecture in detail as well as architectural details of trust flow, logging, and error handling.

The chapters are in detail:

#### 1. Introduction to This Document

This chapter contains an overview of the document as well as terms and definitions and references used in the document.

#### 2. Architectural Overview

This chapter explains the goals for D-RTM of establishing, maintaining and attesting to a Trusted Computing Base. It describes underlying concepts at a high level to help readers understand the overall architecture.

# 3. Trusted Computing Base

This chapter enumerates and describes hardware and software components or processes that are generally involved in establishing and maintaining a Trusted Computing Base on a system. Each description is augmented with information relevant for this specification, such as implementation best practices or potential vulnerabilities. It provides the requirements necessary for each component or process to be compliant with this specification.

#### 4. Structures

This chapter describes the syntax and meaning of data structures and their fields involved in the D-RTM. Subsequent sections define how the structures are used.

#### 5. System States, Transitions, and Interfaces

This chapter defines the system states relevant for the D-RTM process. It identifies transitions between the states. For each transition, it lists the interface used and the required system state for the transition to occur.

## 6. PCR Usage

This chapter describes the D-RTM PCR and how they are used. It defines the Dynamic Core Root of Trust for Measurement (D-CRTM) and provides some examples of different implementations.

#### 7. DCE Requirements

This chapter describes the D-RTM Configuration Environment (DCE) and specifies its requirements.

April 20, 2013 PUBLISHED Page 10 of 93

# 8. Component Setup, Configuration, Validation, and Measurement Required for the D-RTM Process

This chapter specifies the required configuration the DCE must achieve for each hardware or software component involved in establishing a system's Trusted Computing Base during the D-RTM process. It also specifies what validation and measurements must be performed.

#### 9. Event Logging and Reporting

This specifies the D-RTM event log and what measurements are placed in the measurement log during the D-RTM process.

# 1.3 References

- 1. **Trusted Computing Group.** TCG PC Client Specification. [Online] http://www.trustedcomputinggroup.org/developers/pc\_client/specifications.

- 2. ACPI. ACPI Specification, Version 5.0. [Online] http://www.acpi.info.

- 3. **Trusted Computing Group.** TCG Glossary. [Online] https://www.trustedcomputinggroup.org/groups/glossary.

- 4. **Department of Defense.** Department of Defense Standard Department of Defense Trusted Computer System Evaluation Criteria. s.l., United States: Department of Defense, December 26, 1985. DoD 5200.28-STD, Library No. S225,711.

- 5. **Intel.** Extensible Firmware Interface Main Specification Version 1.10. [Online] http://www.intel.com/technology/efi.

- 6. X86 Calling Conventions. *Microsoft Corp.* [Online] http://msdn.microsoft.com/en-us/library/k2b2ssfy.aspx.

- 7. Microsoft Corp. Cdecl. [Online] http://msdn.microsoft.com/en-us/library/zkwh89ks.aspx.

- 8. —. Overview of x64 Calling Conventions. [Online] http://msdn.microsoft.com/en-us/library/ms235286.aspx.

## 1.4 Terms and Definitions

## ACPI (Advanced Configuration and Power Interface)

An open industry specification that describes OS-directed configuration, thermal and power management. ACPI Machine Language code is usually provided as part of the BIOS and interpreted by an operating system-provided interpreter. See reference (2) for more information.

#### **ACPI Namespace**

A hierarchical tree structure in memory that contains named objects loaded from the ACPI tables. See reference (2) for more information.

# AML (ACPI Machine Language)

The binary pseudo-code used to represent ACPI control methods and objects. It is compiled from ASL and is stored for use by the ACPI interpreter in the OS. See reference (2) for more information.

#### ASL (ACPI Source Language)

The programming language equivalent of AML. See reference (2) for more information.

#### BIOS (Basic Input Output System)

Performs basic system configuration and setup and starts the operating software.

April 20, 2013 PUBLISHED Page 11 of 93

## BMC (Baseboard Management Controller)

A specialized controller in many servers used for management tasks (e.g. power management).

## CRTM (Core Root of Trust for Measurement)

The instructions executed by the platform when it acts as the RTM (Root of Trust for Measurement). See reference (3).

## DCE (Dynamic Root of Trust for Measurement Configuration Environment)

The software/firmware that executes from the instantiation of the DL Event to the transfer of control to the Dynamically Launched Measured Environment (DLME). The DCE is responsible for ensuring the platform is in a trustworthy state as defined by the CPU, chipset, and the platform manufacturer.

#### DCE preamble

The PM-provided code that starts the D-RTM process. The entry point to the code is called DL\_Entry. It may perform some initial configuration actions that are platform specific before invoking the D-RTM CPU instruction. Some implementations of the DCE preamble may do some basic validation and return an error code for issues documented in this specification.

## **D-CRTM (Dynamic Core Root of Trust for Measurement)**

The Core Root of Trust for the D-RTM. This is a function that is built into the Host Platform and is started by the Dynamic Launch Event (DL Event). This function is a Trusted Process. Even though the D-CRTM executes after the S-CRTM, the D-RTM's transitive trust chain will not necessarily have a trust dependency on the S-CRTM's transitive trust chain.

#### DLME (Dynamically Launched Measured Environment)

The software executed after the DCE- instantiated TCB is established. The DLME would nominally be supplied by an OS vendor.

#### DMA mapping

Controls how hardware devices access Host Platform memory; requests to access a specific physical memory address may be mapped to an alternate physical memory address. Similar to user mode processes use of virtual memory where page tables control the mapping to physical memory pages. Examples are IOMMU or VT-d.

#### DMA protections

Provide a mechanism to allow a Host Platform to prevent hardware devices from accessing certain Host Platform memory. Examples are a DMA exclusion scheme or DMA mapping.

## DRT (D-RTM Resources Table)

An ACPI table. It holds information such as the location of the D-RTM event log and is the primary way information is passed from the DCE to the DLME. It is used before the D-RTM event to provide the location and address mode of the PM-provided DCE preamble, which starts the D-RTM process.

## **D-RTM** (Dynamic Root of Trust for Measurement)

A platform-dependent function that initializes the state of the platform and provides a new instance of a root of trust for measurement without rebooting the platform. The initial state establishes a minimal Trusted Computing Base.

#### Dynamic Launch (DL)

Describes the process of starting a software environment at an arbitrary time in the runtime of a system.

#### **Dvnamic Launch Event (DL Event)**

A platform dependent event that triggers the D-RTM, ending the Gap, and starting the DCE (or enters remediation). The implementation specific details of the event are encapsulated within the DCE

April 20, 2013 PUBLISHED Page 12 of 93

preamble. In many implementations the event is a privileged CPU instruction, often executed through microcode.

## Dynamic Operating System Environment

The environment in which the DLME executes.

#### Gap

Any untrusted code that is executed after the initial S-RTM and before the Dynamic Launch Event.

#### Hardware attack

Any attack that requires physical access to the machine and changes to the hardware configuration of the machine, but not made using externally accessible interfaces on the platform. For example, plugging a device into a USB port is not a hardware attack.

## Identity Mapped Pages

Memory pages where the virtual page addresses are mapped to the same physical page addresses.

## Integrity Logging

The storage of integrity metrics in a log for later use. See reference (3).

## Integrity Measurement (Metrics)

The process of obtaining metrics of platform characteristics that affect the integrity (trustworthiness) of a platform, and putting digests of those metrics in shielded locations (called Platform Configuration Registers: PCR). See reference (3).

#### Integrity Reporting

The process of attesting to the contents of integrity storage. See reference (3).

## Legacy BIOS

Platform firmware that follows the conventions of early PC/AT-based clients and servers.

#### Locality

A mechanism for supporting a privilege hierarchy in the platform. See reference (3).

#### Manifest

Contains information, including a hash, about a collection of components. If the hash of each component is equal to its corresponding value in the manifest, then the hash of the manifest represents the combined hash of all of the components. Additionally, if the manifest is signed, the signature covers all of the components. The primary advantages of a manifest are that it links multiple components into a single, compact representation, and it allows multiple components that are either unsigned, or signed by different parties, to have a single signature.

## NHP (Non-Host Platform)

A device or controller that cannot be excluded from the TCB. An NHP with immutable firmware is a *Fixed-NHP*, otherwise it is an *updateable NHP*.

#### os

Operating system software that is executed after the firmware, for the purposes of this specification it includes both traditional OSes and virtualization software such as hypervisors.

## PCR (Platform Configuration Register)

A shielded location containing a digest of integrity measurements. See reference (3).

April 20, 2013 PUBLISHED Page 13 of 93

#### PCR.Authorities

The signing authority of platform measurements made during the DCE process is placed in a PCR designated as the PCR. Authorities. The intention of this PCR is to have measurements that only change if an authority for a DCE component changes. For example, a change through a DCE update that was still signed by the platform manufacturer would not impact this PCR measurement.

#### PCR.Details

Details of platform measurements made during the DCE process are placed in a PCR designated as the PCR. Details. The intention of this PCR is to have measurements that change if any minutia of the D-RTM process changes. For example, a change through a DCE update would cause this measurement to change.

#### Peripheral

A device or controller that can be excluded from the TCB. A peripheral can be restricted from accessing the memory of the TCB through DMA protections or other means. A peripheral that is part of the TCB can be restricted from accessing TCB memory outside the peripheral, and must protect any memory within the peripheral.

#### Platform Manufacturer Validated Code

Validated code that is under the authority of the platform manufacturer.

#### Platform owner

The platform owner is used as defined by the TCG glossary (see (3)).

The platform owner is the entity responsible for the platform's security and privacy policies that is distinguished by knowledge of the owner authorization data. As an enhancement to (3), the owner is also the entity, which is authorized to update BIOS, firmware, etc., on the hardware platform. The platform owner is also the entity, which can enter the admin portion of the platform setup utility. See reference (3).

#### Platform user

The platform user is used as defined by the TCG glossary (see (3)).

The platform user is the entity that is making use of the TPM capabilities. See reference (3).

#### PM (Platform Manufacturer)

The platform manufacturer is the entity that has the final responsibility of the trust properties of the platform. It is typically the PM's logo on the platform.

Due to the complex nature of manufacturing relationships, the term OEM is not sufficient or can be misleading when addressing the manufacturer of a platform in the context of this document.

#### PMAM (PM Authority Module)

The authority for the platform manufacturer.

#### Pre-Boot Environment

The time after platform reset when the platform is executing initialization code necessary to load an operating system. This is also called the BIOS and can be either a legacy BIOS or UEFI.

#### Pre-Gap

The time during the S-RTM when the platform security state is completely under the control of the platform manufacturer and is trusted. In this time period, the platform manufacturer may perform actions that are dependencies for the DCE validation process. An example action is loading, measuring, and locking System Management Mode (SMM).

#### Remediation

The actions taken by the platform when it is not possible to perform a Dynamic Launch.

April 20, 2013 PUBLISHED Page 14 of 93

## Root of Trust (component)

A component that must always behave in the expected manner because its misbehavior cannot be detected. A complete set of Roots of Trust has at least the minimum set of functions to enable a description of the platform characteristics that affect the trustworthiness of the platform.

#### RSM (Return from System Management Mode)

This is the instruction invoked by the System Management Interrupt (SMI) handler to return to non-SMM execution. It is the "IRET" analog for SMI.

#### RTM (Root of Trust for Measurement)

A computing engine capable of making inherently reliable integrity measurements. Typically this is the normal platform computing engine, controlled by the CRTM. This is the root of the chain of transitive trust.

#### RTR (Root of Trust for Reporting)

A computing engine capable of reliably reporting information held by the Root of Trust for Storage.

#### RTS (Root of Trust for Storage)

A computing engine capable of maintaining an accurate summary of values of integrity digests and the sequence of digests.

#### S-CRTM (Static Core Root of Trust for Measurement)

An immutable portion of the Host Platform that is required to begin at the Host Platform Reset. This is where the Host Platform begins its execution. See reference (3).

#### S-RTM OS Present Environment

The environment in which the post S-RTM OS executes, as defined in the PC Client Conventional BIOS specification.

#### Sensitive Resource

A hardware resource that must be protected in order for software to defend its Trusted Computing Base.

#### SM Base (System Management Base)

The per logical processor base of CPU System Management Mode (SMM) operation. This is configured by BIOS POST on S5 and S3 boot paths.

#### SMI (System Management Interrupt)

A non-maskable interrupt that transitions the CPU from non-System Management Mode (SMM) operation into SMM operation. It is an OS transparent interrupt that is serviced by BIOS. All context save and restore is handled either by hardware or by BIOS software as part of the handler.

#### SMI Entry Point (System Management Interrupt Entry Point)

This is offset from SMBASE where the SMI Handler will begin execution when it begins servicing an SMI.

#### SMI Handler (System Management Interrupt Handler)

The code that executes when servicing an SMI. This is normally code placed into SMRAM during BIOS POST.

#### SMI Initialization (System Management Interrupt Initialization)

The BIOS POST process that configures both the CPU SMBASE and SMRAM configuration and contents.

April 20, 2013 PUBLISHED Page 15 of 93

# SMI Trap (System Management Interrupt Trap)

The system may implement a set of conditions that result in an SMI. For example, the chipset can be set to generate an SMI on access to an I/O port by system software. This facilitates both software interfaces to the SMI Handler and hardware work-around capabilities.

#### SMM (System Management Mode)

An operating mode of the CPU in which all bus cycles accessing memory are tagged with an "in SMM" indicator. The CPU may internally enable other capabilities based on this state. The chipset may also bind certain capabilities to SMM. SMM is implementation-specific to the CPU.

## SMM/SMRAM Protections (System Management Mode / System Management RAM Protections)

The collection of memory controller features that preclude access to SMRAM by non-SMM entities. It includes bus cycle steering based on an "in SMM" attribute, DMA protection, and configuration locking.

## SMRAM (System Management RAM)

A region of memory that is sequestered in hardware in a manner that it is only decoded by CPU cycles that are tagged with an "in SMM" indicator. SMRAM is implementation-specific to the memory controller.

#### Software attack

An attack that can be mounted using software only or externally accessible interfaces (e.g., boot from a different media, network interfaces). A software attack can be done remotely or locally.

#### S-RTM (Static Root of Trust for Measurement)

The executable component of the RTM that gains control of the Host Platform upon a Host Platform Reset. For a more detailed description, refer to the *TCG PC Client Specific Implementation Specification For Conventional BIOS*.

#### TCB (Trusted Computing Base)

The heart of a trusted computer system. The TCB "contains all of the elements of the system responsible for supporting the security policy and supporting the isolation of objects (code and data) on which the protection is based. The bounds of the TCB equate to the 'security perimeter' referenced in some computer security literature. In the interest of understandable and maintainable protection, a TCB should be as simple as possible consistent with the functions it has to perform. Thus, the TCB includes hardware, firmware, and software critical to protection and must be designed and implemented such that system elements excluded from it need not be trusted to maintain protection. Identification of the interface and elements of the TCB along with their correct functionality therefore forms the basis for evaluation." See reference(4).

#### TPM (Trusted Platform Module)

An implementation of the functions defined in the TCG Trusted Platform Module Specification; the set of Roots of Trust with shielded locations and protected capabilities. Normally includes just the RTS and the RTR. See reference (3).

#### Transitive trust

Also known as "inductive trust." In this process, the Root of Trust gives a trustworthy description of a second group of functions. Based on this description, an interested entity can determine the trust it is to place in this second group of functions. If the interested entity determines that the trust level of the second group of functions is acceptable, the trust boundary is extended from the Root of Trust to include the second group of functions. In this case, the process can be iterated. The second group of functions can give a trustworthy description of the third group of functions, etc. Transitive trust is used to provide a trustworthy description of platform characteristics.

April 20, 2013 PUBLISHED Page 16 of 93

#### Trust

Trust is the expectation that a device will behave in a particular manner for a specific purpose.

## **UEFI** (Unified Extensible Firmware Interface)

The next generation BIOS standard. It defines a new model for the interaction between OS software and platform hardware. See reference (5).

## Validation component

Platform specific code that performs the steps necessary to validate a part of the trustworthiness of a platform or a segment of code.

#### Validated code

Code is considered to be validated when it is assured that the code to be executed is the code that the current authority intended to be run.

April 20, 2013 PUBLISHED Page 17 of 93

# 2 Architectural Overview

## 2.1 Introduction

The Trusted Computing Base (TCB) is a fundamental concept in computer security. It is the portion of the system that is relied on to enforce the security policy of the platform. Two goals of Trusted Computing Group (TCG) technology are to be able to prove that the TCB was properly established and to allow access to sealed data only if the TCB was properly established.

For the Static Root of Trust for Measurement (S-RTM), measurements are taken during the boot process with the intent of being able to demonstrate, through Platform Configuration Registers (PCR), what software was run during the boot process. This reflects the fact that every software component in the boot path has the potential to modify the TCB of the loaded operating system (OS).

A property of the S-RTM sequence is that the evaluation of the TCB of an OS has a dependency on software/firmware that has no ongoing role in the operation of the platform. Software that is loaded, run, and discarded during the boot process must be evaluated to determine if it could or did compromise the TCB.

The purpose of the Dynamic Root of Trust for Measurement (D-RTM) is to reduce the complexity of the TCB so that evaluation of the platform state becomes more tractable.

The method of D-RTM is relatively simple. It is observed that a new chain of trust can be started if

- 1) all processors are placed in a known state,

- 2) a processor begins running measured code, and

- 3) the code that the processor has measured cannot be modified except as directed by the measured code running on the processor.

These conditions are met at system reset when the CPU and the rest of the chipset are forced to an initial condition by a hardware signal; system reset is the way in which the S-RTM is started. For D-RTM, the same three conditions are met but without requiring that the full system be reset.

New instructions have been added to PC processors that cause the CPU to extend the hash of a block of code to the Trusted Platform Module (TPM). Before, or during, the measurement of this code, it is protected from Direct Memory Action (DMA) access either by locking it in the CPU cache or by extending DMA protections over the code in memory. Protecting the code from DMA ensures that it can't be modified after it is measured and before it is executed. The processor then begins execution of the measured code, starting the D-RTM chain of trust.

An essential difference between the D-RTM chain and the S-RTM chain is that the D-RTM chain can start with the platform hardware already configured and with memory prepopulated with an OS. Thus, it is not necessary to rerun all of the software/firmware that was used to configure the hardware or load the OS. If the code is not run, then it is excluded from the TCB as long as any possible effect of that code on the TCB can be negated.

The way in which the D-RTM process neutralizes any possible impact of the boot code is to check to see that the hardware configuration is in a TCB-safe state. That is, it must check to see that the hardware is set up in such a way that the TCB can protect itself. This check is possible because the CPU command that started the D-RTM chain has protected the code doing this check so that no hardware settings can subvert the checks.

## 2.2 DMA

If it was necessary to check every piece of hardware attached to the system in order to ensure that they were in a TCB-safe mode, then D-RTM would likely be more complex than S-RTM. This level of checking would be necessary if the D-RTM TCB could not prevent DMA attacks on its code. So that this kind of checking is not necessary, the D-RTM specification requires that the system has a method of protecting

April 20, 2013 PUBLISHED Page 18 of 93

memory from DMA access. Some example methods are a simple DMA exclusion scheme or by DMA remapping as provided by an IOMMU or VT-d. Since the TCB can prevent DMA access to TCB memory, peripherals cannot change the TCB no matter how the peripherals are programmed. This effectively excludes all of the peripherals from the TCB so their state does not have to be validated. Exclusion of the peripherals from the TCB also excludes the software or firmware that may have programmed those peripherals during the boot process.

In principle, the minimal amount of checking during the Dynamic Root of Trust for Measurement Configuration Environment (DCE) would be to validate that the DMA remapping units were on and preventing all DMA access. Then the DCE could measure some portion of the OS and jump to it, turning the hardware TCB over to the OS. However, this minimal TCB would not be adequate for most modern PCs because of hardware variability and System Management Mode (SMM).

# 2.3 System Management Mode (SMM)

SMM is used by platform manufacturers to control portions of the hardware independent of the OS. The functions of SMM vary but some of the functions are necessary for system reliability and safety (for example, it is common for SMM to be used to prevent thermal damage to the system). SMM may have many privileges that could be used to compromise the TCB. An example of a way SMM could subvert a TCB is to modify memory. SMM has the ability to modify any portion of memory, including the memory used for the OS's TCB. This means that SMM must be included in the evaluation of the state of the TCB performed in the DCE. This specification defines the acceptable methods of validating SMM and NHPs.

## 2.4 Non-Host Platforms

Many systems include controllers (examples include service processors, management engines, and Baseboard Management Controllers, or BMCs) that perform critical platform functions such as power management and platform configuration. These controllers may impact the TCB (platform, DCE, or DLME) in various ways.

Many of these controllers interact with the system (i.e., access the TCB's memory) through DMA or other means, which can be restricted using DMA or similar protection. A controller that can be excluded from the TCB using DMA protection, or other means, is a *peripheral*. A controller that cannot be excluded from the TCB (e.g., can access the TCB's memory) without being subject to DMA or similar protection is called a *Non-Host Platform* or NHP.

To summarize (for the purposes of this specification):

- 1) A controller that can be restricted from reading or writing the platform, DCE, or DLME TCB's memory or control registers using DMA protection (or other means) is called a *peripheral*.

- A controller that cannot be restricted from reading or writing the platform, DCE, or DLME TCB's memory or control registers using DMA protection (or other means) is a *Non-Host Platform* (*NHP*).

Some NHPs have fixed firmware while others may be field programmable. Fixed firmware is loaded by the NHP's manufacturer or the platform manufacturer (PM) and cannot be changed or updated in the field (i.e. immutable). From a TCB perspective, these components are indistinguishable from hardware logic gates and are therefore part of the TCB provided by the platform. These are called *fixed-NHP*s. Fixed-NHPs are assumed to be part of the platform's hardware without analysis by the D-RTM process. They are, therefore, outside the scope of this specification.

Some NHPs are field reprogrammable (i.e., after the controller is either manufactured or placed onto the platform by the platform manufacturer) and are called *updatable NHP*s.

April 20, 2013 PUBLISHED Page 19 of 93

## 2.5 TCB Hardware Protection

In order for the TCB to be able to defend itself after it gets control at the end of the D-RTM process, it must have information about the hardware that is used to protect the TCB. Examples of this hardware are the CPUs, the DMA remapping units, and memory controllers. If the TCB does not control all of this essential hardware, then that hardware could be used to penetrate the TCB. The specification requires that the D-RTM process validate the Advanced Configuration and Power Interface (ACPI) tables that describe the TCB hardware so that the software TCB can have the information necessary to defend itself. Because the TCB hardware on a platform may include components the software TCB has no knowledge about (for example, a new hardware component may have been invented after the software TCB was released to market), the TCB hardware information validated during the D-RTM process contains a list of Sensitive Resources (memory addresses) to which the TCB must restrict access to prevent malicious components from subverting a TCB.

# 2.6 Advanced Configuration and Power Interface (ACPI)

Besides providing a description of the system hardware, ACPI provides methods for controlling various parts of the system hardware. These methods are expressed in an ACPI Machine Language (AML) in, or referenced by, the ACPI tables. On some systems, this interpreted code must access hardware that protects the TCB. This specification details how the D-RTM process will validate the tables containing the ACPI methods so that the software TCB can make an informed decision about whether an ACPI method should be able to modify TCB hardware. In some systems, such as clients, it is not necessary for any ACPI method to modify any TCB hardware. For those systems, the D-RTM provides a validated flag so that the TCB may know it can simply block all access to TCB hardware by ACPI methods.

## 2.7 Authorities

Another significant difference between S-RTM and D-RTM is the method of measurement. S-RTM only records measurement of the actual hashes of code and data. This means that the measurements change each time the code changes even if there is no change in the trust property of the software. D-RTM uses an additional scheme—it records the actual hashes of code and data in one PCR (PCR.Details), but it also records the hash of the "responsible party" for the code in a different PCR (PCR.Authorities). Because the authorities for a particular platform would not normally change over the lifetime of a platform, this scheme allows stability in sealing if only the PCR.Authorities is used.

Normally, the code that checks the hardware TCB (CPU, chipset, and the SMM code) would not change over the lifetime of a platform. On the rare occasion when the code does change, it still comes from the same responsible party. Keeping the authorities measurements unchanged during updates provides stability in the measurements that indicate the state of the TCB.

Because the D-RTM process-created TCB only involves a few measurements, it is relatively simple to evaluate the trustworthiness of the platform: Do you trust the CPU vendor, the chipset vendor, the platform vendor, and the operating system vendor? The PCR.Details allows someone to make more detailed evaluations, but knowing that the authorities approve of the hardware TCB settings is usually sufficient to allow the operating system to boot to a trustworthy state.

## 2.8 PCR Measurements

The Static Core Root of Trust for Measurement begins recording measurements into PCR at the beginning of the boot process. Code running later is unable to tamper with the earlier measurements recorded in the S-RTM PCR. This prevents code from extending the S-RTM PCR to arbitrary values.

The D-RTM process starts when the DL\_Entry call executes. On some platform implementations, it is possible for software to extend the D-RTM PCR values before executing the DL Event. To prevent software from extending the D-RTM PCR to arbitrary values, the PCR begin with an initial value of negative 1 (all bits set). Only by executing the DL Event may the platform reset the D-RTM PCR.Details

April 20, 2013 PUBLISHED Page 20 of 93

and PCR.Authorities to zero. Immediately after resetting the values to zero, the D-RTM process records measurements into the PCR. Because the D-RTM process resets the PCR, if the D-RTM process is invoked multiple times during the same platform boot cycle, each invocation's measurements will be reflected in the resulting D-RTM PCR irrespective of the D-RTM PCR values before the invocation.

## 2.9 DCE and the DCE Preamble

The D-RTM process validation of the state of the TCB hardware occurs in the D-RTM Configuration Environment (DCE). An operating system-provided loader places operating system code (which may include a hypervisor) in memory and then invokes platform-specific code called the DCE preamble to prepare the platform for the D-RTM process. The function entry point a platform should use to invoke the preamble is specified in an ACPI table called the D-RTM Resources Table (DRT). Different hardware platforms may require specific actions before initiating the D-RTM process. The DCE preamble allows platform manufacturers to incorporate any setup work that is necessary for their platform. The DCE preamble then invokes the D-RTM process (DL Event) using an architecture-specific operation (e.g., a CPU instruction).

The DCE preamble is not significant from a security perspective. If an operating system invoked the architecture-specific CPU command to start the D-RTM process directly, the process would succeed only if all the required D-RTM validation steps were successful. Nonetheless, due to characteristics specific to the platform, executing the CPU command to start D-RTM directly without using the DCE preamble may cause the D-RTM process to fail. In summary, OSes do not need to support invoking an architecture-specific operation to start D-RTM directly and the D-RTM process must only succeed if the platform passes the validation performed by the D-RTM process.

The DCE will perform validation of the TCB hardware and TCB firmware (including SMM and relevant ACPI tables), make entries in the D-RTM event log to indicate the authorities and methods used for the validations, and extend the PCR.Details and PCR.Authorities. The DCE validation process is active in that the DCE may decide to correct anything which might cause validation to fail instead of simply detecting the failure and entering failure remediation.

This document specifies the interfaces for entry into the DCE preamble and for the DCE exit to the OS-provided code (the Dynamically Launched Measured Environment or DLME). The specification also outlines the functional requirements of the DCE, but does not mandate an implementation for a DCE. This is because the DCE varies according to processor architecture and there are many viable implementations. When possible, this document will provide suggested implementation options for the DCE in order to illustrate the expected behavior and to encourage use of implementations that are known to have the correct security properties.

# 2.9.1 The "Gap"

The D-RTM process changes the platform from a potentially undefined software and hardware state to a state that has a known hardware configuration and that executes measured code. For convenience, the undefined software and hardware state prior to the D-RTM process is referred to as the "Gap." This term is used to indicate that, because of the unknown properties of the code, there is a Gap in the understanding of the trust state of the platform. A system running in the Gap may be trustworthy, but the complexity of evaluation of the trust state can be nearly intractable. Once a system enters the Gap, the only way to leave is through a successful D-RTM launch or a system reset.

A system may be completely locked down with no ability to add or remove hardware components and with all code in the boot path evaluated and found to be trustworthy. This is not the typical PC. One of the great advantages of a PC is its flexibility and configurability by people with limited technical capabilities. When someone adds a device to their system, they may have implicit trust in the device without knowing whether or not the device is trustworthy. So, a system could ship with all of the components (hardware and software) completely understood by the platform manufacturer from a trust perspective, but as the system is customized (e.g., adding a peripheral) the initial trustworthiness established by the platform manufacturer may be lost and a Gap established.

April 20, 2013 PUBLISHED Page 21 of 93

D-RTM allows establishment of an attestable TCB even if the system starts in a state with completely unknown security properties—it's in the Gap. The platform manufacturer's implementation must establish the TCB and it is important that the implementation is not able to be influenced by actions that occur during the Gap.

The Gap occurs sometime after a power on reset and before the DCE. There is no simple test for determining when the Gap starts but generally upon execution of the first software/firmware component not validated by the PM, the system is considered to have entered the Gap. However, the system may be in the Gap if it is running code that is from the PM, but the PM has chosen not to evaluate the trust properties of the code.

If necessary, a platform manufacturer may set up or record information used later by the DCE to validate the platform before entering the Gap, but only if the data is unable to be altered by actions in the Gap.

What is included in the Gap depends on how the D-RTM process does platform state verification. For example, if the DCE will validate SMM by direct inspection, then the code that loads SMM may be considered to be Gap code and not in the TCB. However, if the DCE checks that SMM was validated when it was initially loaded and locked, then all of the S-RTM code that runs before SMM is locked is Pre-Gap code and becomes part of the final TCB.

## 2.9.2 Timeline

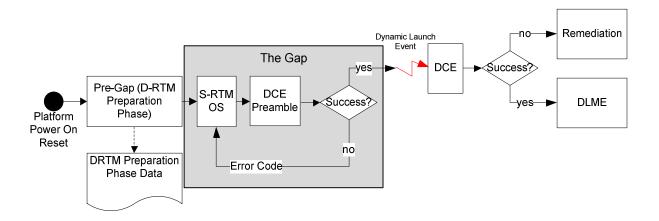

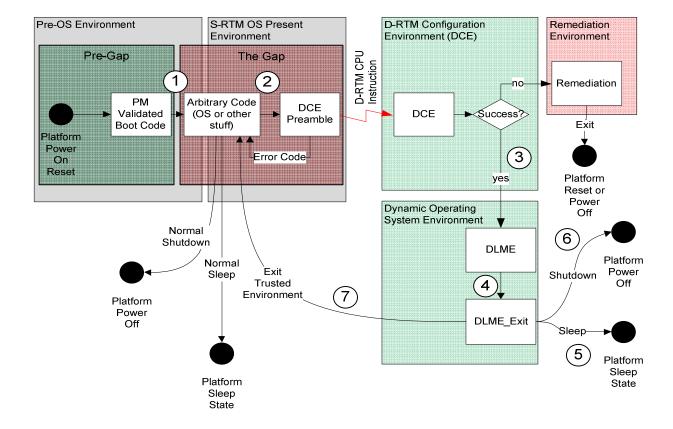

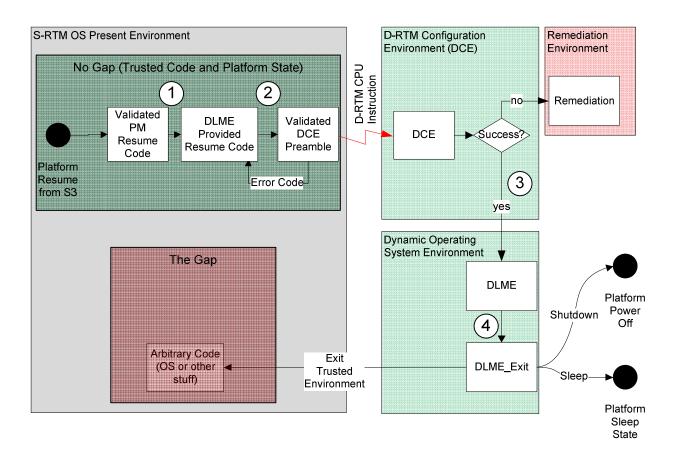

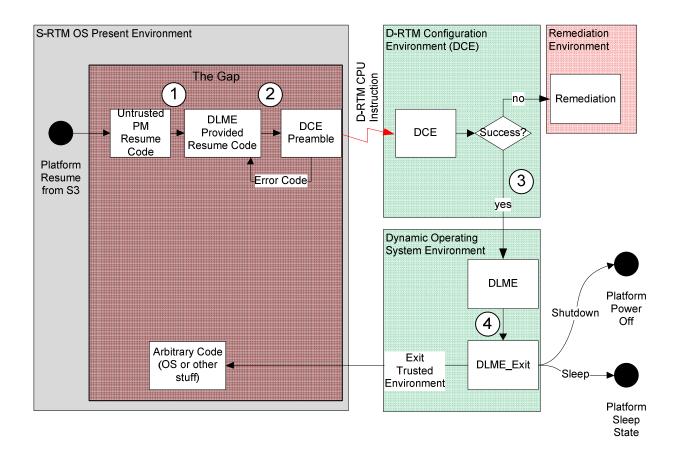

Figure 1 shows a nominal timeline for starting a system with D-RTM. At system reset, an S-RTM chain of trust is started and extended as the BIOS executes. This is the Pre-Gap time period and the platform security state is known completely to the platform manufacturer. The BIOS may load the System Management RAM (SMRAM) area and lock it. If the DCE is going to rely on the S-RTM to validate SMM when loaded and lock it to protect it, then the load and locking actions would need to occur prior to the system entering the Gap. If the DCE is going to independently validate or repopulate SMM, then the initial provisioning of SMRAM would not need to occur before the system enters the Gap.

In the Pre-Gap time period, the BIOS code may also sequester information critical for trust validation (e.g., a portion of the ACPI tables) by copying it to SMRAM before it is locked. The information is then available later when the DCE validates the platform.

On some implementations, the platform manufacturer will not perform any actions that are dependencies for the D-RTM process, and the Pre-Gap period will not exist.

Figure 1 shows the Gap between the Pre-Gap and the DCE preamble. The Gap may contain an arbitrary amount of code from any source and there is no upper limit on the time between startup and the start of the DCE preamble. The Gap could be limited to a small amount of BIOS code or could be a full operating system.

Code in the Gap initiates the D-RTM process by invoking the DCE preamble and passing the location and size of the DLME. The DCE preamble is started by a function call to an entry point that is described in the D-RTM Resources Table. The DCE preamble performs actions provided by the platform manufacturer to help prepare the system to execute the Dynamic Launch (DL) Event in Figure 1. If the DCE preamble determines the platform is not ready to invoke the D-RTM event, it may return an error code to the caller. Otherwise, the DCE preamble concludes by causing the DL Event. This is a CPU-specific command that starts the DCE by measuring an initial piece of code into PCR.Details and PCR.Authorities. This starts the D-CRTM chain of trust.

After the DL Event, the DCE process will ensure that actions taken in the Gap will not influence the TCB of the OS DLME code launched by the DCE.

The DCE will effectively instantiate various verification agents. Each agent will validate the trust state of a specific component (e.g., an agent provided by the CPU vendor validates the setup of the CPU and an agent provided by the PM validates SMM and the ACPI Name Space).

April 20, 2013 PUBLISHED Page 22 of 93

Figure 1 — System Timeline

When the DCE completes successfully, the platform's components are in a state that the chipset and platform manufacturing authorities believe to be trustworthy, as defined by this specification.

If the DCE detects an uncorrectable error in the configuration, it is expected that the DCE will cap the PCR. Authorities and PCR. Details by extending an error value into each D-RTM PCR and execute some PM-provided remediation code or reset the platform. The architecture of the DCE is such that the need for remediation is symptomatic of faulty hardware or an attack. In either case, remediation by the OS is not considered practical.

The DCE will extend detailed measurements of the DLME into PCR. Details and authority measurements for the DLME into the PCR. DLME. Authority.

It should be noted that the DCE timeline and behavior described above is for the DCE provided by the PM. A PM may provide a mechanism for a non-PM-provided DCE to be substituted and executed. This would result in the TPM having different measurements in the PCR.Authorities, and secrets that were sealed to the PM DCE PCR.Authorities values would not be accessible.

#### 2.9.3 Conclusion

The D-RTM process puts the platform in a state that the platform manufacturer validates and that runs measured code. The PCR.Authorities and PCR.Details permit the measured code to access sealed data and prove the TCB was properly established. Based on the initial platform state and information passed to the DLME, it can continue to maintain a TCB by protecting its own memory, restricting access to Sensitive Resources, and controlling the platform configuration.

April 20, 2013 PUBLISHED Page 23 of 93

# 3 Trusted Computing Base

## 3.1 Introduction

This section defines key components that may be elements of the Trusted Computing Base (TCB) central to the D-RTM. Each component is defined and its requirements to comply with this specification are enumerated. If a platform implements the component described, the implementation SHALL conform to the requirements.

# 3.2 DMA (Direct Memory Access)

When devices have access to all of the system memory through DMA, then those devices are part of the hardware TCB. It is a goal of this specification that DMA devices not be included in the TCB.

To eliminate DMA from the hardware TCB, the software TCB must be able to prevent DMA devices from accessing portions of memory that are used by the TCB. The most common mechanisms are *exclusion* or *remapping*.

Exclusion uses a bitmap to prevent access to specific pages of memory. The TCB may SET or CLEAR bits in the bitmap to prevent DMA from accessing a specific page.

Remapping (e.g., an IOMMU or VT-d) uses page tables to limit access to system memory in a way that is similar to memory management of for CPUs.

# 3.2.1 DMA Requirements

The system shall provide a DLME-controllable mechanism for excluding DMA from selected portions of memory.

Some systems allow specific devices access to reserved portions of memory (e.g., video). If the memory allocation can be changed after system initialization, the registers used for allocation must be included in the Sensitive Resources List. Additionally, the DCE shall validate that these dedicated memory allocations do not use memory that is identified in the Sensitive Resources List as being memory available for use by the TCB.

Capabilities the PM must provide the DLME are described in the following table.

| #  | Capabilities the PM must provide to the DLME                                                                                              |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1. | The platform SHALL provide the DLME the ability to turn on DMA remapping and buses without a Gap in its ability to control memory access. |  |

| 2. | All devices on the platform SHALL have DMA remapping coverage.                                                                            |  |

# 3.3 System Management Mode

Some hardware platforms use a System Management Mode (SMM) for low-level platform hardware events and other events that need to be handled by platform firmware. Some examples are

- shutting down a system if it is in danger of overheating,

- handling chipset errors,

- · memory hot adds and memory failover, and

April 20, 2013 PUBLISHED Page 24 of 93

IO bus or IO adapter hot adds.

When a System Management Interrupt (SMI) occurs, the following takes place.

- 1) Normal execution stops.

- 2) The CPU state is saved.

- 3) The CPU enters a high-privilege SMM mode.

- 4) The SMM code associated with the SMI interrupt executes.

- 5) Upon completion, SMM code causes the CPU to exit SMM mode.

- 6) The CPU state is restored to its pre-SMM state and normal, less-privileged execution resumes.

While in System Management Mode, a CPU usually executes with an elevated level of privilege that permits it to access all memory. Virtual memory protections and DMA remapping protections do not apply to SMM code. SMM code can usually go anywhere and do anything on a CPU. SMM implementations are platform manufacturer-specific.

BIOS code early in the startup process loads SMM code into System Management RAM (SMRAM) and locks the SMRAM area so it is accessible only by a processor running in SMM. On hardware platforms with multiple processors, one processor may enter SMM while the other processors are executing normally. On some systems, SMM may be used to control very security-sensitive operations like firmware updates to the Core Root of Trust for Measurement.

While a processor is executing in SMM, if the SMM code jumps to code outside of SMRAM, it too executes with elevated privileges because the process is still in SMM. This can lead to very serious security breaches.

# 3.3.1 Protecting SMM

The SMM code and data residing in the SMRAM, when present, are considered to be part of the Trusted Computing Base (TCB) provided by the platform manufacturer. SMM code must defend itself at all times. DMA operations from IO devices and untrusted Non-Host Platforms (NHPs) SHALL never be allowed to update SMRAM.

The S-RTM SHALL place the SMM code in SMRAM and lock it. The DCE SHALL consider SMM to be "correct by construction." The SMM implementation SHALL successfully maintain its code and data integrity indefinitely.

#### 3.3.1.1 The SMM Threat

Due to the properties of SMM, running malicious code in SMM mode may permit near complete ownership of the hardware platform that is potentially undetectable and in some hardware architectures may even be able to persist across power cycles. Platform manufacturers must be extremely careful to implement appropriate safeguards for their SMM implementations. Any exploit of SMM on a hardware platform may permanently invalidate trust in the hardware platform.

## 3.3.1.2 SMRAM Locking Details

SMRAM SHALL be locked to stop potentially malicious code from being copied into SMRAM. SMRAM must be locked during the Pre-Gap time period while the platform manufacturer has a complete understanding of the system security state. Allowing code the platform manufacturer has not validated to execute prior to locking SMM is not permitted. Once the SMRAM area is locked (including the time after the D-RTM event) the SMM code must continue to protect itself.

April 20, 2013 PUBLISHED Page 25 of 93

## 3.3.1.3 SMM Overlays

An overlay is SMM code that is known to the PM prior to loading the SMM code space. When SMRAM is limited, adequate SMRAM space may not be available to load the entire SMM code base. In this case, the PM may break the code into segments that are loaded on an as-needed basis. The segments are overlaid in SMRAM when SMM code needs to execute the code in the segment. For example, the code to perform a platform manufacturer-controlled SMM update may not be permanently resident in SMM and only be loaded when an update is to be performed. The SMM segments not stored in SMRAM lack the protections provided to SMRAM when SMM is locked. SMM overlays are a case of an SMM callout. Anytime an SMM overlay is used, it must be verified beforehand.

SMM overlays execute in one of two scenarios.

- 1) Overlays are brought into SMRAM post D-RTM event (code incorporation).

- 2) Overlays are too large for the SMRAM area (hardware limitation), must reside outside of SMRAM, and be verified every time they are run, and must be protected from DMA by DMA remapping set up by post D-RTM code (code callout).

#### 3.3.1.4 SMM Rollback

The BIOS, DCE, and SMM will typically be packaged together in an update. These components are susceptible to rollback attacks when an attacker tries to put older versions of weaker code onto a system. Platform manufacturers SHOULD prevent rollback attacks.

## 3.3.2 SMM Requirements

## 3.3.2.1 SMM Integrity

Because SMM has the ability to influence or control the state of the TCB, the platform manufacturer SHALL ensure the integrity of SMM is always maintained.

#### 3.3.2.2 SMM Protections

The platform manufacturer SHALL ensure that the SMRAM is protected by hardware against attacks.

- The PM and the hardware supplier SHALL make sure all SMM protections exist and are enabled (i.e., cache attacks, SMM memory is locked, Flash ROM enables, etc.).

- Any code the SMM calls SHALL be trusted. All SMRAM protections SHALL be in place before entering the Gap and remain in place thereafter.

- DMA operations by peripherals cannot modify the SMRAM area.

## 3.3.2.3 Permitted Implementations of SMRAM Lock

An SMM lock SHALL be implemented. The SMRAM SHALL only be unlocked by a platform reset.

#### 3.3.2.4 SMM Overlays

If SMM uses overlays, the manifest containing the hashes of all overlays must have been stored in SMRAM and recorded in PCR[0]. On each load of an overlay into SMRAM, SMM SHALL validate the overlay against the stored manifest.

#### 3.3.2.5 SMM Callouts

SMM SHALL NOT perform callouts.

April 20, 2013 PUBLISHED Page 26 of 93

#### **3.3.2.6 SMM Updates**

SMM SHALL be updated through a secure update process (typically as part of a secure BIOS update).

After updating the SMM image in SMRAM, the platform SHALL be reset before the new image can be executed.

## 3.4 Non-Host Platforms

Modern platforms typically consist of one or more main CPUs that perform the majority of the computation tasks associated with the platform. The primary operating system or hypervisor and applications execute on these main CPUs, and the security properties of the platform depend primarily on the interaction between various software layers and the architectural features of the main CPUs. This primary platform is often called the Host Platform because it "hosts" or provides a foundation for one or more operating system images.

NHPs may exist within, or attached to, the Host Platform as discussed in Section 2.4 above. NHPs usually consist of a separate CPU or microcontroller that executes software or firmware that is autonomous from the primary operating system, hypervisor, and applications. In some cases SMM allows an independent software entity to use the resources of the primary CPU in ways that are independent of the main operating system or hypervisor. While SMM can be considered an NHP, it is so prevalent and commonly used that this specification treats it separately; for the purpose of this specification, SMM is not an NHP.

As mentioned in Section 2.4, if the access control mechanisms of the host's TCB can defend the TCB from the controller using the DMA protection, then that controller is considered to be a peripheral and not an NHP. If the TCB cannot defend itself from the controller using DMA protection, the controller is an NHP.

Some of these NHPs may provide information about the integrity of their field programmable firmware that may be useful for the TCB to evaluate. However, if an NHP can influence the measurement or verification process, there is little to no value in attempting to obtain the measurement or perform the verification because, by definition, the NHP is outside the protections provided by the DMA protection. Means other than DMA protection may be provided by the platform but are neither specified nor required by this specification. Further, some updatable programmable NHPs have the ability to affect memory configuration even from the CPU's point of view. DMA protection will not be sufficient here to protect the DCE's measurement or verification process from the NHP. For this reason, the verification of NHPs may be performed by the DCE but is not mandated by this specification.

If the state of an updatable NHP can be reliably reported by the DCE, then it is a DCE-verifiable NHP. If the DCE cannot reliably report on an NHP, then it is a DCE-unverifiable NHP. If a DCE-unverifiable NHP has been compromised, there is no way for the DCE to verify if any mitigations for such an NHP are in place. The categories for NHP then are: hardware, DCE-verifiable, and DCE-unverifiable. A peripheral is by definition not a NHP.